Security News

Research

Data Theft Repackaged: A Case Study in Malicious Wrapper Packages on npm

The Socket Research Team breaks down a malicious wrapper package that uses obfuscation to harvest credentials and exfiltrate sensitive data.

GitHub repository: https://github.com/alexforencich/cocotbext-pcie

PCI express simulation framework for cocotb.

Installation from pip (release version, stable):

$ pip install cocotbext-pcie

Installation from git (latest development version, potentially unstable):

$ pip install https://github.com/alexforencich/cocotbext-pcie/archive/master.zip

Installation for active development:

$ git clone https://github.com/alexforencich/cocotbext-pcie

$ pip install -e cocotbext-pcie

See the tests directory, verilog-pcie, and corundum for complete testbenches using these modules.

The core PCIe simulation framework is included in cocotbext.pcie.core. This framework implements an extensive event driven simulation of a complete PCI express system, including root complex, switches, devices, and functions, including support for configuration spaces, capabilities and extended capabilities, and memory and IO operations between devices. The framework includes code to enumerate the bus, initialize configuration space registers and allocate BARs, route messages between devices, perform memory read and write operations, allocate DMA accessible memory regions in the root complex, and handle message signaled interrupts. Any module can be connected to a cosimulated design, enabling testing of not only isolated components and host-device communication but also communication between multiple components such as device-to-device DMA and message passing.

Models of the Xilinx UltraScale and UltraScale+ PCIe hard cores are included in cocotbext.pcie.xilinx.us. These modules can be used in combination with the PCIe BFM to test an HDL design that targets Xilinx UltraScale, UltraScale+, or Virtex 7 series FPGAs, up to PCIe gen 3 x16 or PCIe gen 4 x8. The models currently only support operation as a device, not as a root port.

Models of the Intel Stratix 10 H-Tile/L-Tile PCIe hard cores are included in cocotbext.pcie.intel.s10. These modules can be used in combination with the PCIe BFM to test an HDL design that targets Intel Stratix 10 GX, SX, TX, and MX series FPGAs that contain H-Tiles or L-Tiles, up to PCIe gen 3 x16. The models currently only support operation as a device, not as a root port.

Models of the Intel P-Tile PCIe hard cores are included in cocotbext.pcie.intel.ptile. These modules can be used in combination with the PCIe BFM to test an HDL design that targets Intel Stratix 10 DX or Agilex F series FPGAs that contain P-Tiles, up to PCIe gen 4 x16. The models currently only support operation as a device, not as a root port.

FAQs

PCI express simulation framework for cocotb

We found that cocotbext-pcie demonstrated a healthy version release cadence and project activity because the last version was released less than a year ago. It has 1 open source maintainer collaborating on the project.

Did you know?

Socket for GitHub automatically highlights issues in each pull request and monitors the health of all your open source dependencies. Discover the contents of your packages and block harmful activity before you install or update your dependencies.

Security News

Research

The Socket Research Team breaks down a malicious wrapper package that uses obfuscation to harvest credentials and exfiltrate sensitive data.

Research

Security News

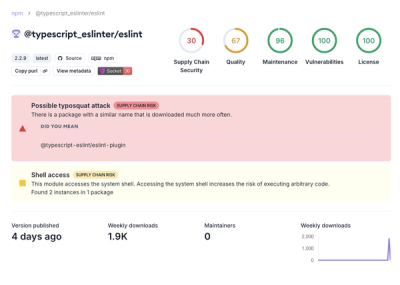

Attackers used a malicious npm package typosquatting a popular ESLint plugin to steal sensitive data, execute commands, and exploit developer systems.

Security News

The Ultralytics' PyPI Package was compromised four times in one weekend through GitHub Actions cache poisoning and failure to rotate previously compromised API tokens.