Security News

Research

Data Theft Repackaged: A Case Study in Malicious Wrapper Packages on npm

The Socket Research Team breaks down a malicious wrapper package that uses obfuscation to harvest credentials and exfiltrate sensitive data.

TAPA is a dataflow HLS framework that features fast compilation, expressive programming model and generates high-frequency FPGA accelerators.

TAPA explicitly decouples communication and computation for better QoR.

TAPA integrates the AutoBridge floorplanner to optimize the RTL generation process.

TAPA achieves 2× higher the frequency on average compared to Vivado. 1

TAPA compiles 7× faster than Vitis HLS. 2

TAPA provides 3× faster software simulation than Vitis HLS.2

TAPA provides 8× faster RTL simulation than Vitis.

[in-progress] TAPA is integrating RapidStream that is up to 10× faster than Vivado.3

TAPA extends the Vitis HLS syntax for richer expressiveness at the C++ level.

TAPA provides dedicated APIs for arbitrary external memory access patterns.

TAPA allows users to explicitly specify parallelism.

In addition to static burst analysis, TAPA supports runtime burst detectuion by transparently merging small memory transactions into large bursts.

TAPA significantly reduce the area overhead of HBM interface IPs compared to Vitis HLS.

TAPA includes an automated design space exploration tool to balance the resource pressure and the wire pressure for HBM FPGAs.

TAPA automatically select the physical channel for each top-level argument of your accelerator.

FAQs

Extending High-Level Synthesis for Task-Parallel Programs

We found that tapa demonstrated a healthy version release cadence and project activity because the last version was released less than a year ago. It has 1 open source maintainer collaborating on the project.

Did you know?

Socket for GitHub automatically highlights issues in each pull request and monitors the health of all your open source dependencies. Discover the contents of your packages and block harmful activity before you install or update your dependencies.

Security News

Research

The Socket Research Team breaks down a malicious wrapper package that uses obfuscation to harvest credentials and exfiltrate sensitive data.

Research

Security News

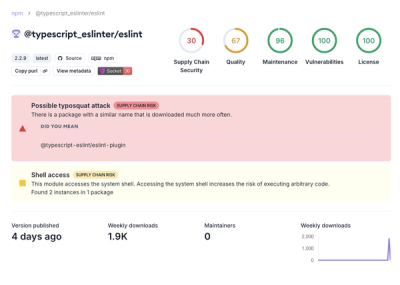

Attackers used a malicious npm package typosquatting a popular ESLint plugin to steal sensitive data, execute commands, and exploit developer systems.

Security News

The Ultralytics' PyPI Package was compromised four times in one weekend through GitHub Actions cache poisoning and failure to rotate previously compromised API tokens.