dw-cache - npm Package Compare versions

Comparing version 0.0.106 to 0.0.107

@@ -1,2 +0,2 @@ | ||

| /*! dw-cache v0.0.106 https://github.com/falsandtru/dw-cache | (c) 2021, falsandtru | (Apache-2.0 AND MPL-2.0) License */ | ||

| /*! dw-cache v0.0.107 https://github.com/falsandtru/dw-cache | (c) 2021, falsandtru | (Apache-2.0 AND MPL-2.0) License */ | ||

| (function webpackUniversalModuleDefinition(root, factory) { | ||

@@ -323,8 +323,13 @@ if(typeof exports === 'object' && typeof module === 'object') | ||

| LRU/CLOCK: | ||

| 性能が低い。 | ||

| LRU: | ||

| 低性能。 | ||

| CLOCK: | ||

| 非常に高速かつLRUよりややヒット率が高い。 | ||

| 容量制限付きマップなどヒット率より速度を優先する場合に最適。 | ||

| ただし最悪時間計算量O(n)。 | ||

| CAR/CDW(CLOCK+DWC)/CLOCK-Pro: | ||

| 最悪計算量がO(n)であるため汎用的でない。 | ||

| CLOCK-ProはCAR同様合計2倍の履歴を持つ。 | ||

| 最悪時間計算量O(n)。 | ||

| CARとCLOCK-Proは合計2倍の履歴を持つ。 | ||

@@ -340,3 +345,3 @@ ARC: | ||

| 情報量(履歴)の不足を補うため全体的に統計精度への依存度が上がっており標本サイズが小さくなるほど | ||

| 情報量(標本がシグナルとなる確率)と統計精度の低下により性能低下しやすくなる。 | ||

| 情報量(標本に含まれるシグナルの比率)の加速的減少と統計精度の低下により性能低下しやすくなる。 | ||

@@ -355,3 +360,3 @@ LIRS: | ||

| 文字列やオブジェクトなどからアドレスを取得または代替値を高速に割り当てる方法がなく汎用的に使用できない。 | ||

| 乱数を代用する方法は強引で低速だがリモートアクセスなど低速な処理では償却可能と思われる。 | ||

| 乱数で代用する方法は強引で低速だがリモートアクセスなど低速な処理では償却可能と思われる。 | ||

| オーバーヘッドが大きくメモ化など同期処理に耐える速度を要件とする用途には適さないと思われる。 | ||

@@ -362,4 +367,3 @@ ブルームフィルタが削除操作不可であるため一定期間内のキャッシュの任意または有効期限超過による | ||

| キャッシュサイズに比例した大きさの遅延が入る。 | ||

| W-TinyLFUの性能は非常に高いがTinyLFUの性能は大幅に低くDWCと一長一短かより悪いうえ | ||

| バーストアクセスに脆弱となるためあらかじめワークロードが検証されている場合以外はDWCのほうが優れている。 | ||

| TinyLFUはバーストアクセスに脆弱であるため基本的にW-TinyLFU以外選択肢に入れるべきではない。 | ||

| メインキャッシュにLRUを使用しているためこれをDWCに置換できる可能性がある。 | ||

@@ -414,3 +418,3 @@ | ||

| capacity: 0, | ||

| window: 2, | ||

| window: 1, | ||

| sample: 1, | ||

@@ -424,5 +428,5 @@ age: Infinity, | ||

| sweep: { | ||

| threshold: 10, | ||

| threshold: 20, | ||

| ratio: 50, | ||

| window: 2, | ||

| window: 1, | ||

| room: 50, | ||

@@ -439,2 +443,3 @@ range: 1, | ||

| this.$size = 0; | ||

| this.injection = 100; | ||

| this.declination = 1; | ||

@@ -453,3 +458,2 @@ if (typeof capacity === 'object') { | ||

| this.partition = capacity - this.window; | ||

| this.injection = 100 * this.declination; | ||

| this.sample = settings.sample; | ||

@@ -497,3 +501,4 @@ this.resource = settings.resource ?? capacity; | ||

| this.partition = this.capacity - this.window; | ||

| this.injection = 100 * this.declination; | ||

| this.injection = 100; | ||

| this.declination = 1; | ||

| this.dict = new Map(); | ||

@@ -535,2 +540,5 @@ this.LRU = new list_1.List(); | ||

| } | ||

| get overflow() { | ||

| return this.overlapLRU * 100 > this.LFU.length * this.sample; | ||

| } | ||

| overlap(entry, eviction = false) { | ||

@@ -550,3 +558,3 @@ if (entry.partition === 'LRU') { | ||

| --this.overlapLRU; | ||

| if (this.declination !== 1 && this.overlapLRU * 100 < this.LFU.length * this.sample) { | ||

| if (this.declination !== 1 && !this.overflow) { | ||

| this.declination = 1; | ||

@@ -572,11 +580,2 @@ } | ||

| } else { | ||

| if (LFU.length > this.partition) { | ||

| let entry = LFU.head.prev; | ||

| entry = entry !== target ? entry : LFU.length !== 1 ? entry.prev : undefined; | ||

| if (entry !== undefined) { | ||

| LFU.delete(entry); | ||

| LRU.unshift(this.overlap(entry)); | ||

| entry.partition = 'LRU'; | ||

| } | ||

| } | ||

| if (LRU.length >= this.window && this.injection === 100 * this.declination) { | ||

@@ -589,3 +588,3 @@ const entry = LRU.head.prev; | ||

| this.injection = 0; | ||

| this.declination = this.overlapLRU * 100 < LFU.length * this.sample ? 1 : (0, alias_1.min)(this.declination * 1.5, 5); | ||

| this.declination = !this.overflow ? 1 : (0, alias_1.min)(this.declination << 1, this.capacity / LFU.length << 3, 8); | ||

| } | ||

@@ -596,2 +595,11 @@ } | ||

| } | ||

| if (LFU.length > this.partition) { | ||

| let entry = LFU.head.prev; | ||

| entry = entry !== target ? entry : LFU.length !== 1 ? entry.prev : undefined; | ||

| if (entry !== undefined) { | ||

| LFU.delete(entry); | ||

| LRU.unshift(this.overlap(entry)); | ||

| entry.partition = 'LRU'; | ||

| } | ||

| } | ||

| if (LRU.length !== 0) { | ||

@@ -658,3 +666,3 @@ victim = LRU.head.prev; | ||

| --this.overlapLRU; | ||

| if (this.declination !== 1 && this.overlapLRU * 100 < this.LFU.length * this.sample) { | ||

| if (this.declination !== 1 && !this.overflow) { | ||

| this.declination = 1; | ||

@@ -784,9 +792,9 @@ } | ||

| class Sweeper { | ||

| constructor(target, capacity, window, room, threshold, ratio, range, shift) { | ||

| constructor(target, capacity, window$, room, threshold, ratio, range$, shift) { | ||

| this.target = target; | ||

| this.window = window; | ||

| this.window$ = window$; | ||

| this.room = room; | ||

| this.threshold = threshold; | ||

| this.ratio = ratio; | ||

| this.range = range; | ||

| this.range$ = range$; | ||

| this.shift = shift; | ||

@@ -801,2 +809,3 @@ this.currWindowHits = 0; | ||

| this.prevRoomMisses = 0; | ||

| this.active = false; | ||

| this.processing = false; | ||

@@ -808,3 +817,3 @@ this.direction = true; | ||

| this.threshold *= 100; | ||

| this.resize(capacity, window, room, range); | ||

| this.resize(capacity, window$, room, range$); | ||

| } | ||

@@ -814,12 +823,19 @@ replace(target) { | ||

| } | ||

| get window() { | ||

| const n = this.target.length > this.window$ << 1 ? 2 : 1; | ||

| return (0, alias_1.max)(this.window$, (0, alias_1.min)(this.target.length >>> n, this.window$ << n + 1)); | ||

| } | ||

| get range() { | ||

| return (0, alias_1.max)(this.range$, (0, alias_1.min)(this.window >>> 1, this.target.length >>> 2)); | ||

| } | ||

| resize(capacity, window, room, range) { | ||

| this.window = (0, alias_1.round)(capacity * window / 100) || 1; | ||

| this.window$ = (0, alias_1.round)(capacity * window / 100) || 1; | ||

| this.room = (0, alias_1.round)(capacity * room / 100) || 1; | ||

| this.range = capacity * range / 100; | ||

| this.range$ = capacity * range / 100; | ||

| this.currWindowHits + this.currWindowMisses >= this.window && this.slideWindow(); | ||

| this.currRoomHits + this.currRoomMisses >= this.room && this.slideRoom(); | ||

| this.active = undefined; | ||

| this.update(); | ||

| } | ||

| clear() { | ||

| this.active = undefined; | ||

| this.active = false; | ||

| this.processing = true; | ||

@@ -845,15 +861,19 @@ this.reset(); | ||

| hit() { | ||

| this.active = undefined; | ||

| ++this.currWindowHits + this.currWindowMisses === this.window && this.slideWindow(); | ||

| ++this.currRoomHits + this.currRoomMisses === this.room && this.slideRoom(); | ||

| ++this.currWindowHits + this.currWindowMisses >= this.window && this.slideWindow(); | ||

| ++this.currRoomHits + this.currRoomMisses >= this.room && this.slideRoom(); | ||

| this.update(); | ||

| this.processing && !this.isActive() && this.reset(); | ||

| } | ||

| miss() { | ||

| this.active = undefined; | ||

| this.currWindowHits + ++this.currWindowMisses === this.window && this.slideWindow(); | ||

| this.currRoomHits + ++this.currRoomMisses === this.room && this.slideRoom(); | ||

| this.currWindowHits + ++this.currWindowMisses >= this.window && this.slideWindow(); | ||

| this.currRoomHits + ++this.currRoomMisses >= this.room && this.slideRoom(); | ||

| this.update(); | ||

| } | ||

| update() { | ||

| if (this.threshold === 0) return; | ||

| const ratio = this.ratioWindow(); | ||

| this.active = ratio < this.threshold || ratio < this.ratioRoom() * this.ratio / 100; | ||

| } | ||

| isActive() { | ||

| if (this.threshold === 0) return false; | ||

| return this.active ??= this.ratioWindow() < (0, alias_1.max)(this.ratioRoom() * this.ratio / 100, this.threshold); | ||

| return this.active; | ||

| } | ||

@@ -904,3 +924,2 @@ ratioWindow() { | ||

| reset() { | ||

| if (!this.processing) return; | ||

| this.processing = false; | ||

@@ -907,0 +926,0 @@ this.direction = true; |

| { | ||

| "name": "dw-cache", | ||

| "version": "0.0.106", | ||

| "version": "0.0.107", | ||

| "description": "The highest performance constant complexity cache algorithm.", | ||

@@ -33,13 +33,13 @@ "private": false, | ||

| "dependencies": { | ||

| "spica": "0.0.761" | ||

| "spica": "0.0.766" | ||

| }, | ||

| "devDependencies": { | ||

| "@types/lru-cache": "7.10.9", | ||

| "@types/mocha": "10.0.3", | ||

| "@types/power-assert": "1.5.10", | ||

| "@typescript-eslint/parser": "^6.10.0", | ||

| "@types/mocha": "10.0.6", | ||

| "@types/power-assert": "1.5.12", | ||

| "@typescript-eslint/parser": "^6.16.0", | ||

| "babel-loader": "^9.1.3", | ||

| "babel-plugin-unassert": "^3.2.0", | ||

| "concurrently": "^8.2.2", | ||

| "eslint": "^8.53.0", | ||

| "eslint": "^8.56.0", | ||

| "eslint-plugin-redos": "^4.4.5", | ||

@@ -54,6 +54,6 @@ "eslint-webpack-plugin": "^4.0.1", | ||

| "karma-power-assert": "^1.0.0", | ||

| "lru-cache": "^10.0.1", | ||

| "lru-cache": "^10.1.0", | ||

| "mocha": "^10.2.0", | ||

| "npm-check-updates": "^16.14.6", | ||

| "ts-loader": "^9.5.0", | ||

| "npm-check-updates": "^16.14.12", | ||

| "ts-loader": "^9.5.1", | ||

| "typescript": "5.2.2", | ||

@@ -60,0 +60,0 @@ "webpack": "^5.89.0", |

464

README.md

@@ -44,6 +44,6 @@ # Dual Window Cache | ||

| |LRU | 16 bytes| 1x| 32 bytes| 100.00%| | ||

| |DWC | 18 bytes| 1x| 34 bytes| 94.11%| | ||

| |ARC | 18 bytes| 2x| 60 bytes| 53.33%| | ||

| |(LIRS) | 35 bytes| 3x| 137 bytes| 23.35%| | ||

| |(LIRS) | 35 bytes| 10x| 438 bytes| 7.30%| | ||

| |DWC | 17 bytes| 1x| 33 bytes| 96.96%| | ||

| |ARC | 17 bytes| 2x| 58 bytes| 55.17%| | ||

| |(LIRS) | 33 bytes| 3x| 131 bytes| 24.42%| | ||

| |(LIRS) | 33 bytes| 10x| 418 bytes| 7.65%| | ||

| |(TinyLFU)| 56 bytes| 1x| 72 bytes| 44.44%| | ||

@@ -59,6 +59,6 @@ |W-TinyLFU| 56 bytes| 1x| 72 bytes| 44.44%| | ||

| |LRU | 16 bytes| 1x| 56 bytes| 100.00%| | ||

| |DWC | 18 bytes| 1x| 58 bytes| 96.55%| | ||

| |ARC | 18 bytes| 2x| 90 bytes| 62.22%| | ||

| |(LIRS) | 35 bytes| 3x| 139 bytes| 40.28%| | ||

| |(LIRS) | 35 bytes| 10x| 363 bytes| 15.42%| | ||

| |DWC | 17 bytes| 1x| 57 bytes| 98.24%| | ||

| |ARC | 17 bytes| 2x| 88 bytes| 63.63%| | ||

| |(LIRS) | 33 bytes| 3x| 203 bytes| 27.58%| | ||

| |(LIRS) | 33 bytes| 10x| 658 bytes| 8.51%| | ||

| |(TinyLFU)| 56 bytes| 1x| 96 bytes| 58.33%| | ||

@@ -74,6 +74,6 @@ |W-TinyLFU| 56 bytes| 1x| 96 bytes| 58.33%| | ||

| |LRU | 16 bytes| 1x| 544 bytes| 100.00%| | ||

| |DWC | 18 bytes| 1x| 546 bytes| 99.63%| | ||

| |ARC | 18 bytes| 2x| 580 bytes| 93.37%| | ||

| |(LIRS) | 35 bytes| 3x| 665 bytes| 81.80%| | ||

| |(LIRS) | 35 bytes| 10x| 1,022 bytes| 53.22%| | ||

| |DWC | 17 bytes| 1x| 545 bytes| 99.81%| | ||

| |ARC | 17 bytes| 2x| 578 bytes| 94.11%| | ||

| |(LIRS) | 33 bytes| 3x| 659 bytes| 82.54%| | ||

| |(LIRS) | 33 bytes| 10x| 1,002 bytes| 54.29%| | ||

| |(TinyLFU)| 56 bytes| 1x| 584 bytes| 93.15%| | ||

@@ -201,4 +201,3 @@ |W-TinyLFU| 56 bytes| 1x| 584 bytes| 93.15%| | ||

| - DWC's results are measured by the same default parameter values. | ||

| - TinyLFU's results are the traces of Ristretto. | ||

| - W-TinyLFU's results are the traces of Caffeine. | ||

| - TinyLFU's results are the traces of Caffeine. | ||

@@ -215,3 +214,2 @@ 1. Set the datasets to `./benchmark/trace` (See `./benchmark/ratio.ts`). | ||

| https://github.com/ben-manes/caffeine/wiki/Efficiency<br> | ||

| https://github.com/dgraph-io/ristretto<br> | ||

| https://docs.google.com/spreadsheets/d/1G3deNz1gJCoXBE2IuraUSwLE7H_EMn4Sn2GU0HTpI5Y (https://github.com/jedisct1/rust-arc-cache/issues/1)<br> | ||

@@ -263,3 +261,3 @@ | ||

| label: 'DWC', | ||

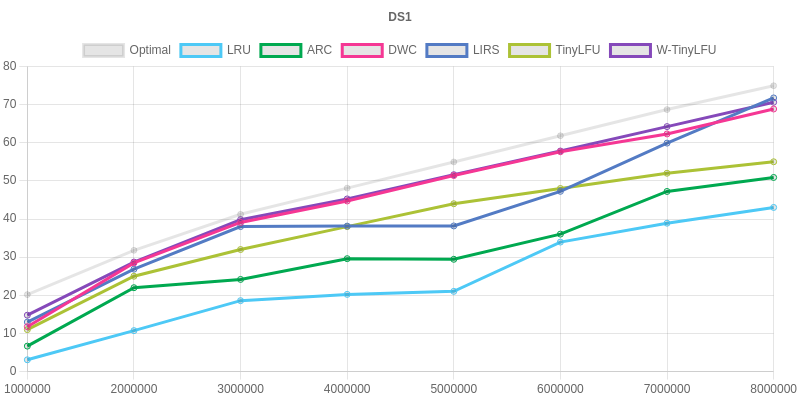

| data: [11.77, 28.50, 39.09, 44.72, 51.39, 57.64, 62.30, 68.83], | ||

| data: [14.73, 27.94, 39.46, 44.20, 50.19, 56.83, 62.55, 70.03], | ||

| borderColor: Utils.color(2), | ||

@@ -273,7 +271,2 @@ }, | ||

| { | ||

| label: 'TinyLFU', | ||

| data: [11, 25, 32, 38, 44, 48, 52, 55], | ||

| borderColor: Utils.color(4), | ||

| }, | ||

| { | ||

| label: 'W-TinyLFU', | ||

@@ -283,2 +276,7 @@ data: [14.79, 28.72, 39.82, 45.26, 51.61, 57.82, 64.22, 70.6], | ||

| }, | ||

| { | ||

| label: 'TinyLFU', | ||

| data: [14.56, 29.01, 39.58, 45.61, 51.02, 57.76, 64.23, 70.52], | ||

| borderColor: Utils.color(4), | ||

| }, | ||

| ] | ||

@@ -288,5 +286,5 @@ }; | ||

|  | ||

|  | ||

| W-TinyLFU > DWC > (LIRS) > (TinyLFU) > ARC > LRU | ||

| W-TinyLFU, (TinyLFU) > DWC > (LIRS) > ARC > LRU | ||

@@ -298,47 +296,47 @@ - DWC is an approximation of W-TinyLFU. | ||

| LRU hit ratio 3.08% | ||

| DWC hit ratio 11.77% | ||

| DWC - LRU hit ratio delta 8.69% | ||

| DWC / LRU hit ratio rate 381% | ||

| DWC hit ratio 14.73% | ||

| DWC - LRU hit ratio delta 11.65% | ||

| DWC / LRU hit ratio ratio 477% | ||

| DS1 2,000,000 | ||

| LRU hit ratio 10.74% | ||

| DWC hit ratio 28.50% | ||

| DWC - LRU hit ratio delta 17.75% | ||

| DWC / LRU hit ratio rate 265% | ||

| DWC hit ratio 27.94% | ||

| DWC - LRU hit ratio delta 17.20% | ||

| DWC / LRU hit ratio ratio 260% | ||

| DS1 3,000,000 | ||

| LRU hit ratio 18.59% | ||

| DWC hit ratio 39.09% | ||

| DWC - LRU hit ratio delta 20.50% | ||

| DWC / LRU hit ratio rate 210% | ||

| DWC hit ratio 39.46% | ||

| DWC - LRU hit ratio delta 20.87% | ||

| DWC / LRU hit ratio ratio 212% | ||

| DS1 4,000,000 | ||

| LRU hit ratio 20.24% | ||

| DWC hit ratio 44.72% | ||

| DWC - LRU hit ratio delta 24.48% | ||

| DWC / LRU hit ratio rate 220% | ||

| DWC hit ratio 44.20% | ||

| DWC - LRU hit ratio delta 23.96% | ||

| DWC / LRU hit ratio ratio 218% | ||

| DS1 5,000,000 | ||

| LRU hit ratio 21.03% | ||

| DWC hit ratio 51.39% | ||

| DWC - LRU hit ratio delta 30.36% | ||

| DWC / LRU hit ratio rate 244% | ||

| DWC hit ratio 50.19% | ||

| DWC - LRU hit ratio delta 29.16% | ||

| DWC / LRU hit ratio ratio 238% | ||

| DS1 6,000,000 | ||

| LRU hit ratio 33.95% | ||

| DWC hit ratio 57.64% | ||

| DWC - LRU hit ratio delta 23.68% | ||

| DWC / LRU hit ratio rate 169% | ||

| DWC hit ratio 56.83% | ||

| DWC - LRU hit ratio delta 22.88% | ||

| DWC / LRU hit ratio ratio 167% | ||

| DS1 7,000,000 | ||

| LRU hit ratio 38.89% | ||

| DWC hit ratio 62.30% | ||

| DWC - LRU hit ratio delta 23.40% | ||

| DWC / LRU hit ratio rate 160% | ||

| DWC hit ratio 62.55% | ||

| DWC - LRU hit ratio delta 23.65% | ||

| DWC / LRU hit ratio ratio 160% | ||

| DS1 8,000,000 | ||

| LRU hit ratio 43.03% | ||

| DWC hit ratio 68.83% | ||

| DWC - LRU hit ratio delta 25.79% | ||

| DWC / LRU hit ratio rate 159% | ||

| DWC hit ratio 70.03% | ||

| DWC - LRU hit ratio delta 26.99% | ||

| DWC / LRU hit ratio ratio 162% | ||

| ``` | ||

@@ -368,3 +366,3 @@ | ||

| label: 'DWC', | ||

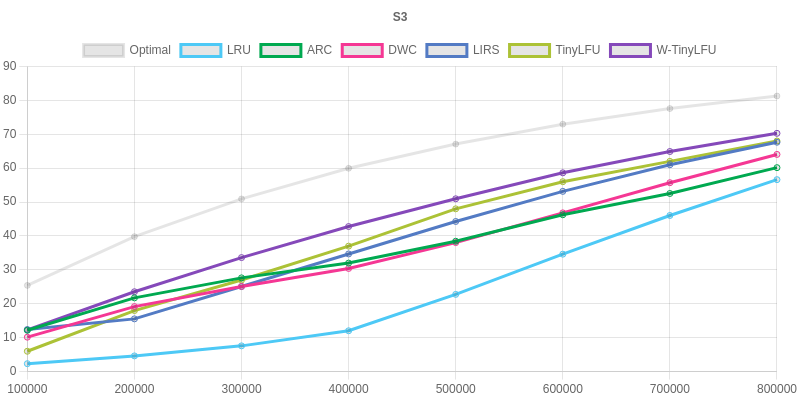

| data: [10.15, 19.17, 25.12, 30.42, 38.04, 46.81, 55.70, 64.04], | ||

| data: [10.14, 20.25, 27.39, 32.69, 38.12, 46.82, 55.71, 64.03], | ||

| borderColor: Utils.color(2), | ||

@@ -378,7 +376,2 @@ }, | ||

| { | ||

| label: 'TinyLFU', | ||

| data: [6, 18, 27, 37, 48, 56, 62, 68], | ||

| borderColor: Utils.color(4), | ||

| }, | ||

| { | ||

| label: 'W-TinyLFU', | ||

@@ -388,2 +381,7 @@ data: [12.29, 23.55, 33.62, 42.77, 50.96, 58.62, 64.9, 70.26], | ||

| }, | ||

| { | ||

| label: 'TinyLFU', | ||

| data: [10.46, 22.68, 33.32, 42.91, 51.35, 59.12, 65.25, 70.6], | ||

| borderColor: Utils.color(4), | ||

| }, | ||

| ] | ||

@@ -393,5 +391,5 @@ }; | ||

|  | ||

|  | ||

| W-TinyLFU > (TinyLFU) > (LIRS) > DWC, ARC > LRU | ||

| W-TinyLFU, (TinyLFU) > (LIRS) > DWC > ARC > LRU | ||

@@ -403,47 +401,47 @@ - DWC is an approximation of ARC. | ||

| LRU hit ratio 2.32% | ||

| DWC hit ratio 10.15% | ||

| DWC - LRU hit ratio delta 7.83% | ||

| DWC / LRU hit ratio rate 436% | ||

| DWC hit ratio 10.14% | ||

| DWC - LRU hit ratio delta 7.81% | ||

| DWC / LRU hit ratio ratio 435% | ||

| S3 200,000 | ||

| LRU hit ratio 4.63% | ||

| DWC hit ratio 19.17% | ||

| DWC - LRU hit ratio delta 14.54% | ||

| DWC / LRU hit ratio rate 414% | ||

| DWC hit ratio 20.25% | ||

| DWC - LRU hit ratio delta 15.61% | ||

| DWC / LRU hit ratio ratio 437% | ||

| S3 300,000 | ||

| LRU hit ratio 7.58% | ||

| DWC hit ratio 25.12% | ||

| DWC - LRU hit ratio delta 17.53% | ||

| DWC / LRU hit ratio rate 331% | ||

| DWC hit ratio 27.39% | ||

| DWC - LRU hit ratio delta 19.80% | ||

| DWC / LRU hit ratio ratio 360% | ||

| S3 400,000 | ||

| LRU hit ratio 12.03% | ||

| DWC hit ratio 30.42% | ||

| DWC - LRU hit ratio delta 18.38% | ||

| DWC / LRU hit ratio rate 252% | ||

| DWC hit ratio 32.69% | ||

| DWC - LRU hit ratio delta 20.65% | ||

| DWC / LRU hit ratio ratio 271% | ||

| S3 500,000 | ||

| LRU hit ratio 22.76% | ||

| DWC hit ratio 38.04% | ||

| DWC - LRU hit ratio delta 15.27% | ||

| DWC / LRU hit ratio rate 167% | ||

| DWC hit ratio 38.12% | ||

| DWC - LRU hit ratio delta 15.35% | ||

| DWC / LRU hit ratio ratio 167% | ||

| S3 600,000 | ||

| LRU hit ratio 34.63% | ||

| DWC hit ratio 46.81% | ||

| DWC - LRU hit ratio delta 12.18% | ||

| DWC / LRU hit ratio rate 135% | ||

| DWC hit ratio 46.82% | ||

| DWC - LRU hit ratio delta 12.19% | ||

| DWC / LRU hit ratio ratio 135% | ||

| S3 700,000 | ||

| LRU hit ratio 46.04% | ||

| DWC hit ratio 55.70% | ||

| DWC hit ratio 55.71% | ||

| DWC - LRU hit ratio delta 9.66% | ||

| DWC / LRU hit ratio rate 120% | ||

| DWC / LRU hit ratio ratio 120% | ||

| S3 800,000 | ||

| LRU hit ratio 56.59% | ||

| DWC hit ratio 64.04% | ||

| DWC - LRU hit ratio delta 7.44% | ||

| DWC / LRU hit ratio rate 113% | ||

| DWC hit ratio 64.03% | ||

| DWC - LRU hit ratio delta 7.43% | ||

| DWC / LRU hit ratio ratio 113% | ||

| ``` | ||

@@ -473,3 +471,3 @@ | ||

| label: 'DWC', | ||

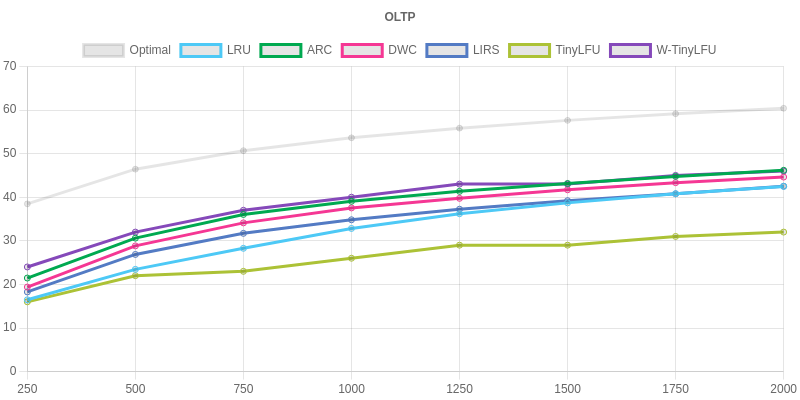

| data: [19.39, 28.83, 34.11, 37.54, 39.74, 41.70, 43.33, 44.62], | ||

| data: [19.59, 29.12, 34.90, 37.93, 39.96, 41.79, 43.43, 44.70], | ||

| borderColor: Utils.color(2), | ||

@@ -483,12 +481,11 @@ }, | ||

| { | ||

| label: 'W-TinyLFU', | ||

| data: [22.76, 29.21, 32.97, 35.3, 37.52, 38.99, 40.37, 41.67], | ||

| borderColor: Utils.color(8), | ||

| }, | ||

| { | ||

| label: 'TinyLFU', | ||

| data: [16, 22, 23, 26, 29, 29, 31, 32], | ||

| data: [15.9, 19.51, 21.9, 24.41, 26.18, 28.65, 30.03, 31.11], | ||

| borderColor: Utils.color(4), | ||

| }, | ||

| { | ||

| label: 'W-TinyLFU', | ||

| // data: [22.76, 29.21, 32.97, 35.3, 37.52, 38.99, 40.37, 41.67], | ||

| data: [24, 32, 37, 40, 43, 43, 45, 46], | ||

| borderColor: Utils.color(8), | ||

| }, | ||

| ] | ||

@@ -498,5 +495,5 @@ }; | ||

|  | ||

|  | ||

| W-TinyLFU > ARC > DWC > (LIRS) > LRU > (TinyLFU) | ||

| ARC > DWC > W-TinyLFU > (LIRS) > LRU > (TinyLFU) | ||

@@ -508,47 +505,47 @@ - DWC is an approximation of ARC. | ||

| LRU hit ratio 16.47% | ||

| DWC hit ratio 19.39% | ||

| DWC - LRU hit ratio delta 2.92% | ||

| DWC / LRU hit ratio rate 117% | ||

| DWC hit ratio 19.59% | ||

| DWC - LRU hit ratio delta 3.11% | ||

| DWC / LRU hit ratio ratio 118% | ||

| OLTP 500 | ||

| LRU hit ratio 23.44% | ||

| DWC hit ratio 28.83% | ||

| DWC - LRU hit ratio delta 5.39% | ||

| DWC / LRU hit ratio rate 122% | ||

| DWC hit ratio 29.12% | ||

| DWC - LRU hit ratio delta 5.68% | ||

| DWC / LRU hit ratio ratio 124% | ||

| OLTP 750 | ||

| LRU hit ratio 28.28% | ||

| DWC hit ratio 34.11% | ||

| DWC - LRU hit ratio delta 5.83% | ||

| DWC / LRU hit ratio rate 120% | ||

| DWC hit ratio 34.90% | ||

| DWC - LRU hit ratio delta 6.62% | ||

| DWC / LRU hit ratio ratio 123% | ||

| OLTP 1,000 | ||

| LRU hit ratio 32.83% | ||

| DWC hit ratio 37.54% | ||

| DWC - LRU hit ratio delta 4.71% | ||

| DWC / LRU hit ratio rate 114% | ||

| DWC hit ratio 37.93% | ||

| DWC - LRU hit ratio delta 5.10% | ||

| DWC / LRU hit ratio ratio 115% | ||

| OLTP 1,250 | ||

| LRU hit ratio 36.20% | ||

| DWC hit ratio 39.74% | ||

| DWC - LRU hit ratio delta 3.53% | ||

| DWC / LRU hit ratio rate 109% | ||

| DWC hit ratio 39.96% | ||

| DWC - LRU hit ratio delta 3.75% | ||

| DWC / LRU hit ratio ratio 110% | ||

| OLTP 1,500 | ||

| LRU hit ratio 38.69% | ||

| DWC hit ratio 41.70% | ||

| DWC - LRU hit ratio delta 3.00% | ||

| DWC / LRU hit ratio rate 107% | ||

| DWC hit ratio 41.79% | ||

| DWC - LRU hit ratio delta 3.09% | ||

| DWC / LRU hit ratio ratio 108% | ||

| OLTP 1,750 | ||

| LRU hit ratio 40.78% | ||

| DWC hit ratio 43.33% | ||

| DWC - LRU hit ratio delta 2.54% | ||

| DWC / LRU hit ratio rate 106% | ||

| DWC hit ratio 43.43% | ||

| DWC - LRU hit ratio delta 2.64% | ||

| DWC / LRU hit ratio ratio 106% | ||

| OLTP 2,000 | ||

| LRU hit ratio 42.46% | ||

| DWC hit ratio 44.62% | ||

| DWC - LRU hit ratio delta 2.16% | ||

| DWC / LRU hit ratio rate 105% | ||

| DWC hit ratio 44.70% | ||

| DWC - LRU hit ratio delta 2.23% | ||

| DWC / LRU hit ratio ratio 105% | ||

| ``` | ||

@@ -578,3 +575,3 @@ | ||

| label: 'DWC', | ||

| data: [16.32, 32.84, 41.35, 49.61, 52.60, 53.78, 55.66, 57.96], | ||

| data: [15.44, 31.53, 41.55, 49.30, 52.42, 53.49, 55.60, 57.96], | ||

| borderColor: Utils.color(2), | ||

@@ -588,7 +585,2 @@ }, | ||

| { | ||

| label: 'TinyLFU', | ||

| data: [18, 26, 40, 46, 51, 54, 55, 57], | ||

| borderColor: Utils.color(4), | ||

| }, | ||

| { | ||

| label: 'W-TinyLFU', | ||

@@ -598,2 +590,7 @@ data: [15.15, 33.08, 43.11, 50.57, 51.87, 53.57, 55.61, 57.96], | ||

| }, | ||

| { | ||

| label: 'TinyLFU', | ||

| data: [16.56, 33.85, 43.86, 50.96, 52.05, 53.57, 55.89, 57.96], | ||

| borderColor: Utils.color(4), | ||

| }, | ||

| ] | ||

@@ -603,5 +600,5 @@ }; | ||

|  | ||

|  | ||

| W-TinyLFU, (LIRS) > DWC > (TinyLFU) >> ARC > LRU | ||

| W-TinyLFU, (TinyLFU), (LIRS) > DWC >> ARC > LRU | ||

@@ -613,41 +610,41 @@ - DWC is an approximation of W-TinyLFU. | ||

| LRU hit ratio 0.93% | ||

| DWC hit ratio 16.32% | ||

| DWC - LRU hit ratio delta 15.39% | ||

| DWC / LRU hit ratio rate 1753% | ||

| DWC hit ratio 15.44% | ||

| DWC - LRU hit ratio delta 14.51% | ||

| DWC / LRU hit ratio ratio 1658% | ||

| GLI 500 | ||

| LRU hit ratio 0.96% | ||

| DWC hit ratio 32.84% | ||

| DWC - LRU hit ratio delta 31.88% | ||

| DWC / LRU hit ratio rate 3406% | ||

| DWC hit ratio 31.53% | ||

| DWC - LRU hit ratio delta 30.56% | ||

| DWC / LRU hit ratio ratio 3270% | ||

| GLI 750 | ||

| LRU hit ratio 1.16% | ||

| DWC hit ratio 41.35% | ||

| DWC - LRU hit ratio delta 40.19% | ||

| DWC / LRU hit ratio rate 3554% | ||

| DWC hit ratio 41.55% | ||

| DWC - LRU hit ratio delta 40.39% | ||

| DWC / LRU hit ratio ratio 3571% | ||

| GLI 1,000 | ||

| LRU hit ratio 11.22% | ||

| DWC hit ratio 49.61% | ||

| DWC - LRU hit ratio delta 38.39% | ||

| DWC / LRU hit ratio rate 442% | ||

| DWC hit ratio 49.30% | ||

| DWC - LRU hit ratio delta 38.08% | ||

| DWC / LRU hit ratio ratio 439% | ||

| GLI 1,250 | ||

| LRU hit ratio 21.25% | ||

| DWC hit ratio 52.60% | ||

| DWC - LRU hit ratio delta 31.34% | ||

| DWC / LRU hit ratio rate 247% | ||

| DWC hit ratio 52.42% | ||

| DWC - LRU hit ratio delta 31.16% | ||

| DWC / LRU hit ratio ratio 246% | ||

| GLI 1,500 | ||

| LRU hit ratio 36.56% | ||

| DWC hit ratio 53.78% | ||

| DWC - LRU hit ratio delta 17.22% | ||

| DWC / LRU hit ratio rate 147% | ||

| DWC hit ratio 53.49% | ||

| DWC - LRU hit ratio delta 16.92% | ||

| DWC / LRU hit ratio ratio 146% | ||

| GLI 1,750 | ||

| LRU hit ratio 45.04% | ||

| DWC hit ratio 55.66% | ||

| DWC - LRU hit ratio delta 10.62% | ||

| DWC / LRU hit ratio rate 123% | ||

| DWC hit ratio 55.60% | ||

| DWC - LRU hit ratio delta 10.55% | ||

| DWC / LRU hit ratio ratio 123% | ||

@@ -658,38 +655,36 @@ GLI 2,000 | ||

| DWC - LRU hit ratio delta 0.54% | ||

| DWC / LRU hit ratio rate 100% | ||

| DWC / LRU hit ratio ratio 100% | ||

| ``` | ||

| <!-- | ||

| ### LOOP | ||

| ``` | ||

| LOOP 100 | ||

| LRU hit ratio 0.00% | ||

| DWC hit ratio 7.46% | ||

| DWC - LRU hit ratio delta 7.46% | ||

| DWC / LRU hit ratio rate Infinity% | ||

| DWC hit ratio 8.12% | ||

| DWC - LRU hit ratio delta 8.12% | ||

| DWC / LRU hit ratio ratio Infinity% | ||

| LOOP 250 | ||

| LRU hit ratio 0.00% | ||

| DWC hit ratio 18.56% | ||

| DWC - LRU hit ratio delta 18.56% | ||

| DWC / LRU hit ratio rate Infinity% | ||

| DWC hit ratio 21.33% | ||

| DWC - LRU hit ratio delta 21.33% | ||

| DWC / LRU hit ratio ratio Infinity% | ||

| LOOP 500 | ||

| LRU hit ratio 0.00% | ||

| DWC hit ratio 41.83% | ||

| DWC - LRU hit ratio delta 41.83% | ||

| DWC / LRU hit ratio rate Infinity% | ||

| DWC hit ratio 44.42% | ||

| DWC - LRU hit ratio delta 44.42% | ||

| DWC / LRU hit ratio ratio Infinity% | ||

| LOOP 750 | ||

| LRU hit ratio 0.00% | ||

| DWC hit ratio 62.78% | ||

| DWC - LRU hit ratio delta 62.78% | ||

| DWC / LRU hit ratio rate Infinity% | ||

| DWC hit ratio 67.62% | ||

| DWC - LRU hit ratio delta 67.62% | ||

| DWC / LRU hit ratio ratio Infinity% | ||

| LOOP 1,000 | ||

| LRU hit ratio 0.00% | ||

| DWC hit ratio 96.78% | ||

| DWC - LRU hit ratio delta 96.78% | ||

| DWC / LRU hit ratio rate Infinity% | ||

| DWC hit ratio 96.77% | ||

| DWC - LRU hit ratio delta 96.77% | ||

| DWC / LRU hit ratio ratio Infinity% | ||

@@ -700,3 +695,99 @@ LOOP 1,250 | ||

| DWC - LRU hit ratio delta 0.00% | ||

| DWC / LRU hit ratio rate 100% | ||

| DWC / LRU hit ratio ratio 100% | ||

| WS1 1,000,000 | ||

| LRU hit ratio 2.95% | ||

| DWC hit ratio 10.37% | ||

| DWC - LRU hit ratio delta 7.42% | ||

| DWC / LRU hit ratio ratio 351% | ||

| WS1 2,000,000 | ||

| LRU hit ratio 6.08% | ||

| DWC hit ratio 18.37% | ||

| DWC - LRU hit ratio delta 12.28% | ||

| DWC / LRU hit ratio ratio 301% | ||

| WS1 3,000,000 | ||

| LRU hit ratio 9.63% | ||

| DWC hit ratio 21.94% | ||

| DWC - LRU hit ratio delta 12.31% | ||

| DWC / LRU hit ratio ratio 227% | ||

| WS1 4,000,000 | ||

| LRU hit ratio 21.59% | ||

| DWC hit ratio 27.22% | ||

| DWC - LRU hit ratio delta 5.62% | ||

| DWC / LRU hit ratio ratio 126% | ||

| WS1 5,000,000 | ||

| LRU hit ratio 33.91% | ||

| DWC hit ratio 37.77% | ||

| DWC - LRU hit ratio delta 3.86% | ||

| DWC / LRU hit ratio ratio 111% | ||

| WS1 6,000,000 | ||

| LRU hit ratio 45.74% | ||

| DWC hit ratio 48.43% | ||

| DWC - LRU hit ratio delta 2.69% | ||

| DWC / LRU hit ratio ratio 105% | ||

| WS1 7,000,000 | ||

| LRU hit ratio 54.89% | ||

| DWC hit ratio 56.74% | ||

| DWC - LRU hit ratio delta 1.85% | ||

| DWC / LRU hit ratio ratio 103% | ||

| WS1 8,000,000 | ||

| LRU hit ratio 61.40% | ||

| DWC hit ratio 62.11% | ||

| DWC - LRU hit ratio delta 0.71% | ||

| DWC / LRU hit ratio ratio 101% | ||

| F1 2,500 | ||

| LRU hit ratio 27.74% | ||

| DWC hit ratio 25.12% | ||

| DWC - LRU hit ratio delta -2.61% | ||

| DWC / LRU hit ratio ratio 90% | ||

| F1 5,000 | ||

| LRU hit ratio 30.55% | ||

| DWC hit ratio 30.20% | ||

| DWC - LRU hit ratio delta -0.35% | ||

| DWC / LRU hit ratio ratio 98% | ||

| F1 7,500 | ||

| LRU hit ratio 32.18% | ||

| DWC hit ratio 33.85% | ||

| DWC - LRU hit ratio delta 1.67% | ||

| DWC / LRU hit ratio ratio 105% | ||

| F1 10,000 | ||

| LRU hit ratio 33.27% | ||

| DWC hit ratio 35.64% | ||

| DWC - LRU hit ratio delta 2.36% | ||

| DWC / LRU hit ratio ratio 107% | ||

| F1 12,500 | ||

| LRU hit ratio 34.19% | ||

| DWC hit ratio 36.73% | ||

| DWC - LRU hit ratio delta 2.54% | ||

| DWC / LRU hit ratio ratio 107% | ||

| F1 15,000 | ||

| LRU hit ratio 34.97% | ||

| DWC hit ratio 37.61% | ||

| DWC - LRU hit ratio delta 2.64% | ||

| DWC / LRU hit ratio ratio 107% | ||

| F1 17,500 | ||

| LRU hit ratio 35.62% | ||

| DWC hit ratio 38.17% | ||

| DWC - LRU hit ratio delta 2.55% | ||

| DWC / LRU hit ratio ratio 107% | ||

| F1 20,000 | ||

| LRU hit ratio 36.17% | ||

| DWC hit ratio 38.80% | ||

| DWC - LRU hit ratio delta 2.63% | ||

| DWC / LRU hit ratio ratio 107% | ||

| ``` | ||

@@ -707,6 +798,4 @@ --> | ||

| 80-120% of [lru-cache](https://www.npmjs.com/package/lru-cache). | ||

| 60-90% of [lru-cache](https://www.npmjs.com/package/lru-cache). | ||

| Note that the number of trials per capacity for simulation 1,000,000 is insufficient. | ||

| No result with 10,000,000 because lru-cache crushes with the next error on the next machine of GitHub Actions. | ||

@@ -723,3 +812,2 @@ It is verified that the error was thrown also when benchmarking only lru-cache. | ||

| Clock: spica/clock<br> | ||

@@ -731,49 +819,49 @@ ISCCache: [lru-cache](https://www.npmjs.com/package/lru-cache)<br> | ||

| ``` | ||

| 'Clock new x 1,328,833 ops/sec ±3.63% (113 runs sampled)' | ||

| 'Clock new x 1,681,457 ops/sec ±1.18% (117 runs sampled)' | ||

| 'ISCCache new x 13,768 ops/sec ±1.00% (120 runs sampled)' | ||

| 'ISCCache new x 17,725 ops/sec ±0.84% (119 runs sampled)' | ||

| 'LRUCache new x 27,168,783 ops/sec ±1.50% (122 runs sampled)' | ||

| 'LRUCache new x 32,201,503 ops/sec ±0.26% (123 runs sampled)' | ||

| 'DW-Cache new x 6,049,201 ops/sec ±0.86% (122 runs sampled)' | ||

| 'DW-Cache new x 6,962,509 ops/sec ±0.28% (123 runs sampled)' | ||

| 'Clock simulation 100 x 13,493,137 ops/sec ±1.65% (121 runs sampled)' | ||

| 'Clock simulation 100 x 20,067,017 ops/sec ±0.27% (122 runs sampled)' | ||

| 'ISCCache simulation 100 x 8,651,793 ops/sec ±1.85% (121 runs sampled)' | ||

| 'ISCCache simulation 100 x 13,461,209 ops/sec ±0.36% (122 runs sampled)' | ||

| 'LRUCache simulation 100 x 10,604,646 ops/sec ±2.24% (120 runs sampled)' | ||

| 'LRUCache simulation 100 x 16,250,516 ops/sec ±0.53% (123 runs sampled)' | ||

| 'DW-Cache simulation 100 x 7,242,013 ops/sec ±1.65% (121 runs sampled)' | ||

| 'DW-Cache simulation 100 x 7,809,927 ops/sec ±0.29% (123 runs sampled)' | ||

| 'Clock simulation 1,000 x 10,694,963 ops/sec ±1.81% (120 runs sampled)' | ||

| 'Clock simulation 1,000 x 16,387,821 ops/sec ±0.73% (123 runs sampled)' | ||

| 'ISCCache simulation 1,000 x 7,700,019 ops/sec ±1.90% (121 runs sampled)' | ||

| 'ISCCache simulation 1,000 x 11,893,246 ops/sec ±0.27% (123 runs sampled)' | ||

| 'LRUCache simulation 1,000 x 9,184,813 ops/sec ±2.13% (120 runs sampled)' | ||

| 'LRUCache simulation 1,000 x 13,991,155 ops/sec ±0.50% (123 runs sampled)' | ||

| 'DW-Cache simulation 1,000 x 7,041,470 ops/sec ±1.77% (120 runs sampled)' | ||

| 'DW-Cache simulation 1,000 x 7,221,664 ops/sec ±0.33% (123 runs sampled)' | ||

| 'Clock simulation 10,000 x 10,517,215 ops/sec ±1.78% (122 runs sampled)' | ||

| 'Clock simulation 10,000 x 14,583,648 ops/sec ±0.51% (123 runs sampled)' | ||

| 'ISCCache simulation 10,000 x 7,365,593 ops/sec ±1.67% (121 runs sampled)' | ||

| 'ISCCache simulation 10,000 x 9,693,221 ops/sec ±0.58% (122 runs sampled)' | ||

| 'LRUCache simulation 10,000 x 8,685,666 ops/sec ±1.81% (121 runs sampled)' | ||

| 'LRUCache simulation 10,000 x 10,558,716 ops/sec ±0.82% (122 runs sampled)' | ||

| 'DW-Cache simulation 10,000 x 7,317,621 ops/sec ±1.42% (120 runs sampled)' | ||

| 'DW-Cache simulation 10,000 x 6,604,530 ops/sec ±0.25% (123 runs sampled)' | ||

| 'Clock simulation 100,000 x 7,417,826 ops/sec ±1.60% (118 runs sampled)' | ||

| 'Clock simulation 100,000 x 8,904,873 ops/sec ±1.76% (118 runs sampled)' | ||

| 'ISCCache simulation 100,000 x 4,523,157 ops/sec ±1.22% (117 runs sampled)' | ||

| 'ISCCache simulation 100,000 x 5,527,676 ops/sec ±1.70% (114 runs sampled)' | ||

| 'LRUCache simulation 100,000 x 5,424,344 ops/sec ±2.10% (119 runs sampled)' | ||

| 'LRUCache simulation 100,000 x 6,309,913 ops/sec ±2.23% (114 runs sampled)' | ||

| 'DW-Cache simulation 100,000 x 4,190,537 ops/sec ±1.44% (113 runs sampled)' | ||

| 'DW-Cache simulation 100,000 x 4,970,814 ops/sec ±2.23% (109 runs sampled)' | ||

| 'Clock simulation 1,000,000 x 4,519,623 ops/sec ±3.63% (106 runs sampled)' | ||

| 'Clock simulation 1,000,000 x 4,708,193 ops/sec ±4.16% (102 runs sampled)' | ||

| 'ISCCache simulation 1,000,000 x 2,081,961 ops/sec ±3.35% (101 runs sampled)' | ||

| 'ISCCache simulation 1,000,000 x 2,396,780 ops/sec ±4.46% (95 runs sampled)' | ||

| 'LRUCache simulation 1,000,000 x 2,686,808 ops/sec ±3.88% (103 runs sampled)' | ||

| 'LRUCache simulation 1,000,000 x 2,290,716 ops/sec ±3.21% (107 runs sampled)' | ||

| 'DW-Cache simulation 1,000,000 x 2,481,012 ops/sec ±2.54% (111 runs sampled)' | ||

| 'DW-Cache simulation 1,000,000 x 2,088,055 ops/sec ±3.22% (110 runs sampled)' | ||

| ``` | ||

@@ -780,0 +868,0 @@ |

Improved metrics

- Total package byte prevSize

- increased by1.85%

115672

- Lines of code

- increased by0.9%

2018

- Number of lines in readme file

- increased by10.81%

902

Dependency changes

+ Addedspica@0.0.766(transitive)

- Removedspica@0.0.761(transitive)

Updatedspica@0.0.766