Security News

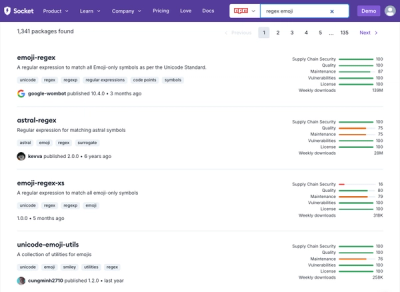

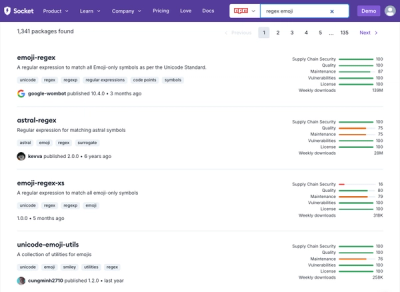

Weekly Downloads Now Available in npm Package Search Results

Socket's package search now displays weekly downloads for npm packages, helping developers quickly assess popularity and make more informed decisions.

RgGen is a code generation tool for ASIC/IP/FPGA/RTL engineers. It will automatically generate source code related to control and status registers (CSR), e.g. SytemVerilog RTL, UVM register model (UVM RAL/uvm_reg), C header file, Wiki documents, from human readable register map specifications.

RgGen has following features:

RgGen is written in the Ruby programing language and its required version is 3.0 or later. You need to install any of these versions of Ruby before installing RgGen tool. To install Ruby, see this page.

RgGen depends on following sub components and other Ruby libraries.

To install RgGen and the dependencies, use the command below:

$ gem install rggen

RgGen and dependencies will be installed on your system root.

If you want to install them on other location, you need to specify install path and set GEM_PATH and PATH environment variables:

$ gem install --install-dir /path/to/your/install/directory rggen

$ export GEM_PATH=/path/to/your/install/directory

$ export PATH=$GEM_PATH/bin:$PATH

You would get the following error message duaring installation if you have the old RgGen (version < 0.9).

ERROR: Error installing rggen:

"rggen" from rggen-core conflicts with installed executable from rggen

To resolve the above error, there are three solutions. See this page

The rggen-docker is a Docker image to simplify installation and use of RgGen. You can also execute RgGen by using this image:

$ docker run -ti --rm -v ${PWD}:/work --user $(id -u):$(id -g) rggendev/rggen-docker:latest -c config.yml -o out block_0.yml

See the rggen-docker repository for further details.

See Wiki documents.

RgGen has plugin feature to allow your cusomization.

See this Wiki document for futher detals.

Following EDA tools can accept the generated source files.

-Wno-unoptflat switch for Verilog RTLYou can get sample configuration file and register map specification from the rggen-sample repository. This register map specification is for a UART IP.

You can try to use RgGen by uisng these example files. Hit command below:

$ rggen -c config.yml -o out uart_csr.yml

-c: Specify path to your configuration file-o: Specify path to the directory where generated files will be written toThen, generated files will be written to the out directory.

If you want to generate Verilog RTL and/or VHDL RTL then you need to instll optional plugins listed below.

$ gem install rggen-verilog

$ gem install rggen-vhdl

In addition, you need to tell RgGen to use these plugins by using the --plugin option switch:

rggen -c config.yml --plugin rggen-verilog --plugin rggen-vhdl uart_csr.yml

RgGen will generate following source files from the uart_csr.yml register map specification:

See Contributing Guide.

Feedbacks, bug reports, questions and etc. are wellcome! You can post them by using following ways:

Copyright © 2019-2024 Taichi Ishitani. RgGen is licensed under the MIT License, see LICENSE for futher detils.

Everyone interacting in the RgGen project’s codebases, issue trackers, chat rooms and mailing lists is expected to follow the code of conduct.

FAQs

Unknown package

We found that rggen demonstrated a healthy version release cadence and project activity because the last version was released less than a year ago. It has 1 open source maintainer collaborating on the project.

Did you know?

Socket for GitHub automatically highlights issues in each pull request and monitors the health of all your open source dependencies. Discover the contents of your packages and block harmful activity before you install or update your dependencies.

Security News

Socket's package search now displays weekly downloads for npm packages, helping developers quickly assess popularity and make more informed decisions.

Security News

A Stanford study reveals 9.5% of engineers contribute almost nothing, costing tech $90B annually, with remote work fueling the rise of "ghost engineers."

Research

Security News

Socket’s threat research team has detected six malicious npm packages typosquatting popular libraries to insert SSH backdoors.