Security News

Research

Data Theft Repackaged: A Case Study in Malicious Wrapper Packages on npm

The Socket Research Team breaks down a malicious wrapper package that uses obfuscation to harvest credentials and exfiltrate sensitive data.

DoVado needs python 3.6 or higher. Install it through pip, on many Linux systems use pip3 to force python 3 installation. Dovado has been tested on Vivado 2018.3.

pip3 install --user --no-cache dovado-rtl

Dovado has two modes:

| parameter | description | mandatory |

|---|---|---|

| –file-path | path to the target file | yes |

| –board | vivado descriptor of a board | yes |

| –parameters | parameters to use either for points/space (integers and booleans supported) | yes |

| –clock-port | RTL identifier of the clock port | yes |

| –implementation | switch to evaluate designs after implementation (default is after synthesis) | no |

| –incremental | switch to use incremental synthesis/implementation | no |

| –directives | list of directives to pass to synthesis, place and route (default is RuntimeOptimized for all three) | no |

| –target-clock | clock (Mhz) to give as a constraint to Vivado (default=1000) | no |

| –metrics | list of metrics to target using their integer identifier (default mode is interactive, you will be asked after first synthesis/implementation) | no |

After those parameters specify points/space both these modes take an argument:

No further parameters can be passed to points

| parameter | description | mandatory |

|---|---|---|

| –power-of-2 | list of ’y/n’ to state whether a parameter must be explored stepping power of 2s | no |

| –many-objective | replace default ga implementation (NSGA-II) with AGEMOEA which is a variant better suited for many objective (e.g. >4) optimization | no |

| –param-initial-values | parameter values which are guaranteed to be synthesizable to retrieve metric mapping | no |

| –optimization-runtime | set as a termination condition a timeout as hh:mm:ss | no |

| –read-design-values | read design values from a csv | no |

| –disable-approximate | disable approximation | no |

| –estimation-model | choose Hoeffding Adaptive Tree (default) or Kernel Ridge regressor or Shadow to not use the controller but log anyways | no |

| –controller-model | choose Mab or Distance-based (default) controller | no |

| –disable-controller-mab-weight | disable loss weighting in distance controller | no |

| –n-controllers | set the number of voting controllers (default is 500, too high for many applications) | no |

Directory structure is vital for the functioning of the tool:

In order to inspect the tool's work you have several files at hand:

dovado_work/point_evaluation.csv which has one design evaluation per line, mapped with the points you give dovado; written online during tool's execution in points modedovado_work/space_exploration.csv which has all the design points explored together with the design values; written online during tool's execution both in points mode and in space modedovado_work/design_space.csv and dovado_work/objective_space.csv are written at the end of the design exploration process (space mode) and contain respectively the pareto set of design parameters and the corresponding evaluationsProcedure:

Create a folder named custom_metrics in the same folder where you are running dovado

mkdir custom_metrics

Create the python file which will contain your custom metric

touch test_metric.py

Write your metric function, any function you need to carry out the computation and any import for the libraries

# here any import works

# e.g. import numpy as np

import numpy as np

def test_metric(**kwargs) -> float:

# only one metric per file is admitted

# if you want another custom metric create a new file

print(kwargs)

return float(__helper_function(kwargs["frequency"]))

def __helper_function(a):

# Care the underscores '__' are mandatory for helper functions

# This function won't show as a metric is here only for helping purposes

return a + 1000

Run dovado without metric selected:

dovado --file-path <path to "neorv32/rtl/neorv32/neorv32_top.vhd"> --board xc7k70tfbv676-1 --parameters MEM_INT_IMEM_SIZE --parameters MEM_INT_DMEM_SIZE --clock-port clk_i space 16384 131072 8129 65536 --power-of-2 y --power-of-2 y

Select your metrics, you will now find your custom metrics after all utilisation metrics provided by your board of choice:

General advice:

the function must return float (highly recommended to annotate the return type)

all helper functions must start with double underscore “__”

relative imports are not supported, use only absolute imports

all subfolders of custom_metrics are ignored.

from the **kwargs you can access all the other board metrics, the frequency and all the parameters you are using for explorationo by using either “frequency”, the name you find above or the parameter name in dovado's call e.g:

kwargs["frequency"]

kwargs["Slice LUTs*"]

kwargs["MEM_INT_IMEM_SIZE"]

neorv32 is an embedded RISC-V core.

git clone https://github.com/stnolting/neorv32

cd neorv32/rtl

mkdir neorv32

cp core/* neorv32/

cp core/mem/neorv32_*.default.vhd neorv32/

sed -i "s/CLOCK_FREQUENCY\s*: natural;\s*-- clock frequency of clk_i in Hz/CLOCK_FREQUENCY :natural:=100000000; -- clock frequency of clk_i in Hz/" neorv32/neorv32_top.vhd

Changing the name of the core folder, which contains all vhdl files, to the name of the package which is used along the files is mandatory to make dovado get ’use’ directives right. Exploring the parameter space of the top module:

dovado --file-path <path to "neorv32/rtl/neorv32/neorv32_top.vhd"> --board xc7k70tfbv676-1 --parameters MEM_INT_IMEM_SIZE --parameters MEM_INT_DMEM_SIZE --clock-port clk_i --metrics 0 --metrics 1 --metrics 4 --metrics 9 space 16384 131072 8129 65536 --power-of-2 y --power-of-2 y

Above we are optimizing two memory parameters (MEMINTIMEMSIZE, MEMINTDMEMSIZE) with clki as the clock port with metrics chosen:

Ranges are specified after space and we also specify that we want to search only among power of 2’s solutions.

Here an example of exploring boolean parameters, the trick here is to explore them as normal parameters but use as range [0, 1] obviously they can be mixed up with non-boolean parameters during exploration:

dovado --file-path <path to "neorv32/rtl/neorv32/neorv32_top.vhd"> --board xc7k70tfbv676-1 --parameters BOOTLOADER_EN --parameters CPU_EXTENSION_RISCV_A --parameters CPU_EXTENSION_RISCV_B --parameters CPU_EXTENSION_RISCV_C --clock-port clk_i --metrics 0 --metrics 1 --metrics 4 --metrics 9 space 0 1 0 1 0 1 0 1 --disable-approximate

corundum is an open-source 100Gbps-NIC.

git clone https://github.com/corundum/corundum

cd corundum/

Exploring the parameter space of the top module:

dovado --file-path <path to "corundum/fpga/common/rtl/cpl_queue_manager.v"> --board xc7k70tfbv676-1 --target-clock 100000 --parameters OP_TABLE_SIZE --parameters QUEUE_INDEX_WIDTH --parameters PIPELINE --clock-port clk --metrics 0 --metrics 1 --metrics 4 --metrics 9 space 8 64 4 11 2 32 --disable-approximate

Using approximation parameters:

dovado --file-path <path to "corundum/fpga/common/rtl/cpl_queue_manager.v"> --board xc7k70tfbv676-1 --target-clock 100000 --parameters OP_TABLE_SIZE --parameters QUEUE_INDEX_WIDTH --parameters PIPELINE --clock-port clk --metrics 0 --metrics 1 --metrics 4 --metrics 9 space 8 64 4 11 2 32

CICERO is a Domain-Specific Architecture (DSA) for Regular Expression matching. We take off-the-shelf DSA and apply a DSE to maximize Frequency and custom metrics, and minimize LUTs usage according to some metrics. The custom metrics employed are performance of the multi-engine architecture and $I cache size by changing Core#, Internal Parallelism, $I lines.

git clone https://github.com/necst/cicero -b feature/dse

mkdir custom_metrics

cp cicero/hdl_src/cicero_core/custom_metrics/avg_perf.py custom_metrics/

cp cicero/hdl_src/cicero_core/custom_metrics/isize.py custom_metrics/

For the exact version run:

dovado --file-path cicero/hdl_src/cicero_core/cicero_core.v --board xcku060-ffva1156-2-i --parameters BB_N --parameters CC_ID_BITS --parameters PC_WIDTH --clock-port s00_axi_aclk --metrics 0 --metrics 1 --metrics 37 --metrics 38 space 2 72 1 3 9 10 --many-objective --disable-approximate

For the approximated version run:

dovado --file-path cicero/hdl_src/cicero_core/cicero_core.v --board xcku060-ffva1156-2-i --parameters BB_N --parameters CC_ID_BITS --parameters PC_WIDTH --clock-port s00_axi_aclk --metrics 0 --metrics 1 --metrics 37 --metrics 38 space 2 72 1 3 9 10 --many-objective

Vivado does not support for 2018.3 release a complex SystemVerilog top-module with a hierarchy. Therefore, we use a simpler module for showcasing purposes.

git clone https://github.com/openhwgroup/cv32e40p

cd rtl

mkdir testing

cp cv32e40p_fifo.sv testing/

In this project an include directory is used but dovado does not currently support it thus we create a subfolder, name may be whatever, where to isolate the module we are interested in studying. This workaround is only possible if the module one wants to study works standalone without include directives.

dovado --file-path <path to "cv32e40p/rtl/testing/cv32e40p_fifo.sv"> --board xc7k70tfbv676-1 --target-clock 100000 --parameters DEPTH --parameters DATA_WIDTH --clock-port clk_i --metrics 0 --metrics 1 --metrics 4 --metrics 9 space 2 4096 2 64 --power-of-2 y --power-of-2 y --disable-approximate

We combined Dovado with Movado capabilities and run DSEs for different purposes and showcasing Movado approximation capabilities. We explore corundum with the corresponding section commands .

Then we explore the RISCV extensions of neorv32, modelling the combination of such extensions with the following custom metric (already written in custom_metrics/extension_score.py):

def extension_score(**kwargs) -> float:

print("kwargs:")

print(kwargs)

return float(__helper_function([int(kwargs["CPU_EXTENSION_RISCV_A"]), int(kwargs["CPU_EXTENSION_RISCV_C"]), int(kwargs["CPU_EXTENSION_RISCV_E"]), int(kwargs["CPU_EXTENSION_RISCV_M"]), int(kwargs["CPU_EXTENSION_RISCV_U"]), int(kwargs["CPU_EXTENSION_RISCV_Zfinx"]), int(kwargs["CPU_EXTENSION_RISCV_Zicsr"]), int(kwargs["CPU_EXTENSION_RISCV_Zifencei"])]))

def __helper_function(variants):

print(variants)

return sum(variants) * -1000.00

and run with

dovado --file-path neorv32/rtl/neorv32/neorv32_ProcessorTop_Minimal.vhd --board xa7a12tcpg238-2I --parameters CPU_EXTENSION_RISCV_A --parameters CPU_EXTENSION_RISCV_C --parameters CPU_EXTENSION_RISCV_E --parameters CPU_EXTENSION_RISCV_M --parameters CPU_EXTENSION_RISCV_U --parameters CPU_EXTENSION_RISCV_Zfinx --parameters CPU_EXTENSION_RISCV_Zicsr --parameters CPU_EXTENSION_RISCV_Zifencei --clock-port clk_i space 0 1 0 1 0 1 0 1 0 1 0 1 0 1 0 1 --disable-approximate

You will be prompted to choose the objective metrics to optimize, where you will be able to select the custom metric. Please remove the final --disable-approximate to run the exact version.

We then explore two DSA for Regular Expressions. We scale up TiReX single core with its internal parallelism, but the project is not open-sourced, hence not replicable here. We then scale out CICERO engines number according to the corresponding examples section procedures.

If you find this repository useful, please use the following citation:

Dovado with custom metrics and Movado:

@inproceedings{paletti2021online,

title={Online Learning RTL Synthesis for Automated Design Space Exploration},

author={Paletti, Daniele and Peverelli, Francesco and Conficconi, Davide and Santambrogio, Marco D},

booktitle={2022 IEEE International Parallel and Distributed Processing Symposium Workshops (IPDPSW)},

year={2022},

organization={IEEE}

}

Original Dovado Publication:

@inproceedings{paletti2021dovado,

title={Dovado: An Open-Source Design Space Exploration Framework},

author={Paletti, Daniele and Conficconi, Davide and Santambrogio, Marco D},

booktitle={2021 IEEE International Parallel and Distributed Processing Symposium Workshops (IPDPSW)},

pages={128--135},

year={2021},

organization={IEEE}

}

FAQs

RTL Design Space Exploration on top of Vivado

We found that dovado-rtl demonstrated a healthy version release cadence and project activity because the last version was released less than a year ago. It has 1 open source maintainer collaborating on the project.

Did you know?

Socket for GitHub automatically highlights issues in each pull request and monitors the health of all your open source dependencies. Discover the contents of your packages and block harmful activity before you install or update your dependencies.

Security News

Research

The Socket Research Team breaks down a malicious wrapper package that uses obfuscation to harvest credentials and exfiltrate sensitive data.

Research

Security News

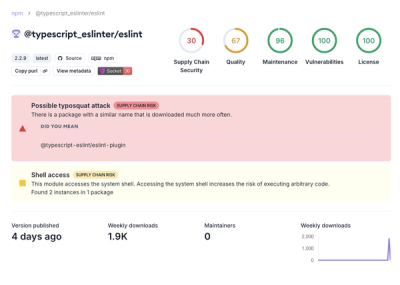

Attackers used a malicious npm package typosquatting a popular ESLint plugin to steal sensitive data, execute commands, and exploit developer systems.

Security News

The Ultralytics' PyPI Package was compromised four times in one weekend through GitHub Actions cache poisoning and failure to rotate previously compromised API tokens.